(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-187172

(P2018-187172A)

(43) 公開日 平成30年11月29日(2018.11.29)

| (51) Int.Cl.   |              | F 1              |         |

|----------------|--------------|------------------|---------|

| <b>A 6 1 B</b> | <b>1/04</b>  | <b>(2006,01)</b> | A 6 1 B |

| <b>A 6 1 B</b> | <b>1/05</b>  | <b>(2006,01)</b> | A 6 1 B |

| <b>A 6 1 B</b> | <b>1/00</b>  | <b>(2006,01)</b> | A 6 1 B |

| <b>G 0 2 B</b> | <b>23/24</b> | <b>(2006,01)</b> | G 0 2 B |

テーマコード (参考)

2H040

4 C 161

680

審査請求 未請求 請求項の数 9 O.L. (全 27 頁)

(21) 出願番号 特願2017-93368 (P2017-93368)

(22) 出願日 平成29年5月9日 (2017.5.9)

(71) 出願人 000000376

オリンパス株式会社

東京都八王子市石川町2951番地

(74) 代理人 100076233

弁理士 伊藤 進

(74) 代理人 100101661

弁理士 長谷川 靖

(74) 代理人 100135932

弁理士 篠浦 治

(72) 発明者 斎藤 匡史

東京都八王子市石川町2951番地 オリ

ンパス株式会社内

F ターム (参考) 2H040 CA04 CA11 CA22 DA02 DA11

DA12 DA14 DA15 DA21 GA02

GA11

最終頁に続く

(54) 【発明の名称】 内視鏡

(57) 【要約】

【課題】撮像素子の起動時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化する。

【解決手段】撮像素子内に配設され、電源から撮像素子に対して所定の電源電圧を供給するためのVDDラインと、撮像素子に設けられ、所定の制御信号に応じてVDDラインに流れる電流を変化させるように当該VDDラインの負荷を補正する電源電流補正部150と、撮像素子に設けられ、撮像素子の起動時においてVDDラインに流れる電流を、撮像素子の通常動作時においてVDDラインに流れる電流に対して相対的に増加させるための所定の制御信号を生成し、所定のタイミングにおいて電源電流補正部150に対して当該制御信号を出力する電源電流制御部160と、を具備する。

【選択図】図 2

## 【特許請求の範囲】

## 【請求項 1】

挿入部の先端部に配設され、被観察体像を撮像する撮像素子と、

前記撮像素子内に配設され、所定の電源から当該撮像素子に対して所定の電源電圧を供給するための電源供給線と、

前記撮像素子に設けられ、所定の制御信号に応じて前記電源供給線に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部と、

前記撮像素子に設けられ、当該撮像素子の起動時において前記電源供給線に流れる電流を、前記撮像素子の通常動作時において前記電源供給線に流れる電流に対して相対的に増加させるための前記所定の制御信号を生成し、所定のタイミングにおいて前記電源電流補正部に対して当該制御信号を出力する電源電流制御部と、

を具備することを特徴とする内視鏡。

## 【請求項 2】

前記電源電流補正部は、前記電源供給線とGND間にに対して、前記撮像素子の起動時と前記撮像素子の通常動作時とにおける前記電源に係る消費電流が略同じになる補正電流を流すよう当該電源供給線の負荷を補正する

ことを特徴とする請求項 1 の内視鏡。

## 【請求項 3】

前記電源電流補正部は、抵抗とトランジスタとを有する補正回路を備え、

前記電源電流制御部は、前記撮像素子の起動時において、前記補正回路における前記トランジスタを導通せしめ、前記抵抗値と当該トランジスタのオン抵抗値とによる前記補正電流を供給する

ことを特徴とする請求項 1 の内視鏡。

## 【請求項 4】

前記電源電流補正部は、

前記撮像素子における撮像信号を出力する出力ドライバ回路と、

前記出力ドライバ回路への入力電圧を切り換え可能とする補正回路と、

と有し、

前記電源電流制御部は、前記撮像素子の起動時において、前記撮像素子の起動時と前記撮像素子の通常動作時とにおける前記電源に係る消費電流が略同じになるように、前記補正回路を制御する

ことを特徴とする請求項 1 の内視鏡。

## 【請求項 5】

前記電源電流補正部は、

前記撮像素子における画素部から出力された画素出力信号を入力し差動撮像信号を出力する差動出力ドライバ回路と、

前記差動出力ドライバの駆動電流を切り換え可能とする補正回路と、

と有し、

前記電源電流制御部は、前記撮像素子の起動時において、前記撮像素子の起動時と前記撮像素子の通常動作時とにおける前記電源に係る消費電流が略同じになるように、前記補正回路を制御する

ことを特徴とする請求項 1 の内視鏡。

## 【請求項 6】

前記補正回路は、前記差動ドライバ回路における前記電源供給線とGNDの間に設けられ、当該差動出力ドライバの駆動電流を変化させる可変電流源である

ことを特徴とする請求項 5 の内視鏡。

## 【請求項 7】

前記補正回路は、前記差動ドライバ回路における前記電源供給線とGNDの間に設けられた、互いに定格電流値の異なる複数の電流源と、当該複数の電流源を切り換える切り換え部と、を有する

ことを特徴とする請求項 5 の内視鏡。

【請求項 8】

前記補正回路は、前記差動ドライバ回路における前記電源供給線と GND の間に設けられたトランジスタと、当該トランジスタに印加する駆動電圧として異なるリファレンス電圧を切り換える切り換え部と、を有する

ことを特徴とする請求項 5 の内視鏡。

【請求項 9】

前記電源電流制御部は、入力する同期信号に基づいて前記撮像素子が起動時である否かを判定する

ことを特徴とする請求項 1 - 8 のいずれか 1 項に記載の内視鏡。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、内視鏡に関し、特に、撮像素子を備える内視鏡に関する。

【背景技術】

【0002】

被検体の内部の被写体を撮像する内視鏡、及び、内視鏡により撮像された被写体の観察画像を生成する画像処理装置等を具備する内視鏡システムが、医療分野及び工業分野等において広く用いられている。

20

【0003】

このような内視鏡システムにおける内視鏡としては、撮像素子として、例えば CMOS イメージセンサを採用し、この CMOS イメージセンサから出力される撮像信号を後段の画像処理装置に対して伝送する内視鏡が広く知られている。

【0004】

上述した CMOS イメージセンサ等の撮像素子は、一般に、画像処理装置から内視鏡内に配設されたケーブルを介して所定の電源電圧の供給を受けると共に、所定の制御信号を受けて駆動されるようになっている。

30

【0005】

ここで、近年、内視鏡に配設される撮像素子および挿入部に関しては、益々小型化・細径化が図られており、これに伴い前記挿入部およびいわゆるユニバーサルコードの内部に配設されるケーブルについても細径化が求められている。

【0006】

このような状況にあるため、撮像素子に対して電源供給するための電源ケーブルについても、できる限り細くすることが求められている。このように電源ケーブルが細くなるとケーブル自体の抵抗成分も大きくなり、場合によっては  $10 \Omega / m$  以上の抵抗値となる。この場合、撮像素子の動作時の消費電力は、例えば、数  $10 \text{ mW}$  (消費電流は数  $10 \text{ mA}$  ) に及ぶことも考えられる。

【0007】

ここで、例えば、電源ケーブル長が  $5 \text{ m}$  となると、ケーブル自体の抵抗値は  $50 \Omega$  となる。この場合、挿入部先端部に配設された撮像素子において通常動作時 (消費電流  $15 \text{ mA}$  ) での電源電圧が  $3.3 \text{ V}$  となるようにするには、電源供給元の電圧は、前記ケーブルの抵抗値を考慮すると約  $4.05 \text{ V}$  に設定する必要がある。

40

【0008】

ところが、一般に CMOS イメージセンサ等の撮像素子は、起動時 (電源投入時) においては動作が安定していないことから、消費電流が通常動作時よりも少なく、例えば、数  $\text{mA}$  (ex.  $4 \text{ mA}$ ) 程度まで減少する場合がある。このように起動時においては予定する (通常動作時を基準とした場合) 消費電流より小さい電流しか流れない虞もあり、この場合、撮像素子には、 $3.3 \text{ V}$  より高い、例えば、 $3.85 \text{ V}$  程度の電圧が印加される虞があり、撮像素子の耐圧をオーバーしてしまうという問題が生じる。

50

【0009】

一方、従来、特開2002-562号公報において、内視鏡の挿入部先端部に配設された撮像素子に対して電源安定化回路を設ける技術が示されている（特許文献1）。

【0010】

また、特開2014-200637号公報においては、内視鏡の先端部におけるCCDを駆動する波形生成回路の動作状態に応じて電源電流を調整することで動作状態の変化による消費電流の変動を抑制する技術が示されている（特許文献2）。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2002-562号公報

10

【特許文献2】特開2014-200637号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

しかし、特許文献1に示される技術においては、安定化回路はセラミックコンデンサなどの素子からなり、過渡的に変化する消費電流分の電荷については供給できるものの、撮像素子の起動時と通常動作時とにおいて消費電流を一定にすることはできない。

【0013】

また、特許文献2に示される技術においては、撮像素子の起動時に動作が決まらない状態において確実に消費電流低減分を補う構成、方法については何等開示されておらず、上述したケーブル細径化による抵抗分増加の影響についても対応することは困難であると考えられる。

20

【0014】

本発明は上述した事情に鑑みてなされたものであり、撮像素子の起動時等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することを可能とした内視鏡を提供することを目的とする。

【課題を解決するための手段】

【0015】

本発明の一態様の内視鏡は、挿入部の先端部に配設され、被観察体像を撮像する撮像素子と、前記撮像素子内に配設され、所定の電源から当該撮像素子に対して所定の電源電圧を供給するための電源供給線と、前記撮像素子に設けられ、所定の制御信号に応じて前記電源供給線に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部と、前記撮像素子に設けられ、当該撮像素子の起動時において前記電源供給線に流れる電流を、前記撮像素子の通常動作時において前記電源供給線に流れる電流に対して相対的に増加させるための前記所定の制御信号を生成し、所定のタイミングにおいて前記電源電流補正部に対して当該制御信号を出力する電源電流制御部と、を具備する。

30

【発明の効果】

【0016】

本発明によれば、撮像素子の起動時等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することを可能とした内視鏡を提供することができる。

40

【図面の簡単な説明】

【0017】

【図1】図1は、本発明の第1の実施形態の内視鏡を含む内視鏡システムの構成を示す図である。

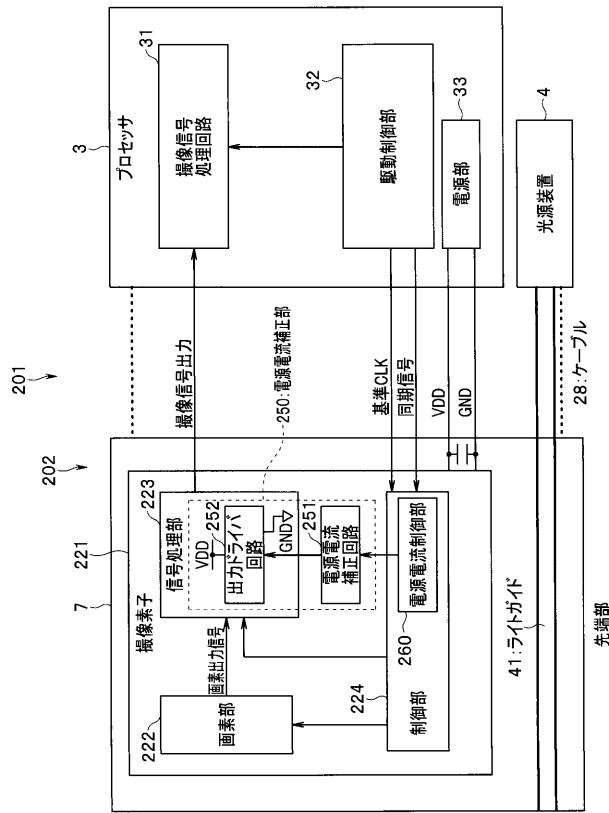

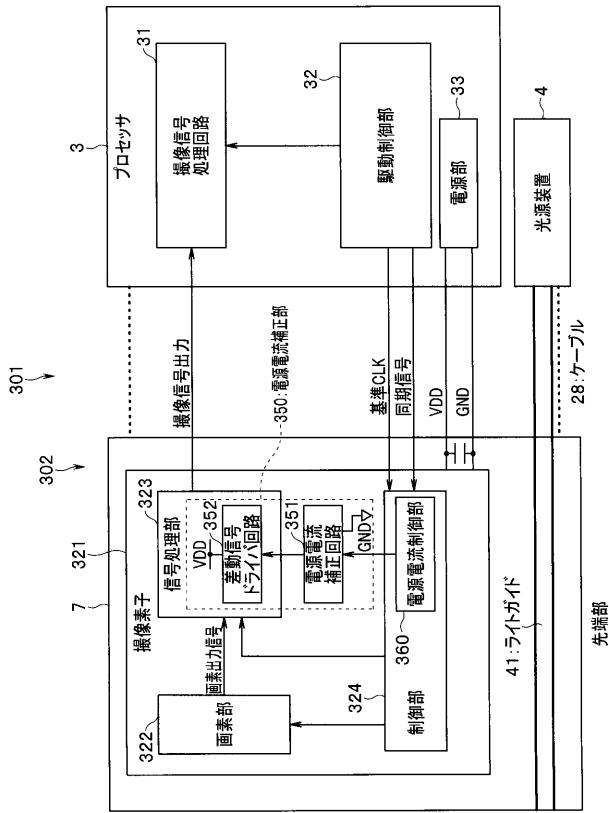

【図2】図2は、第1の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

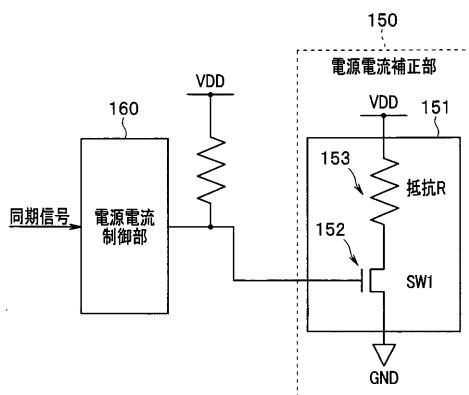

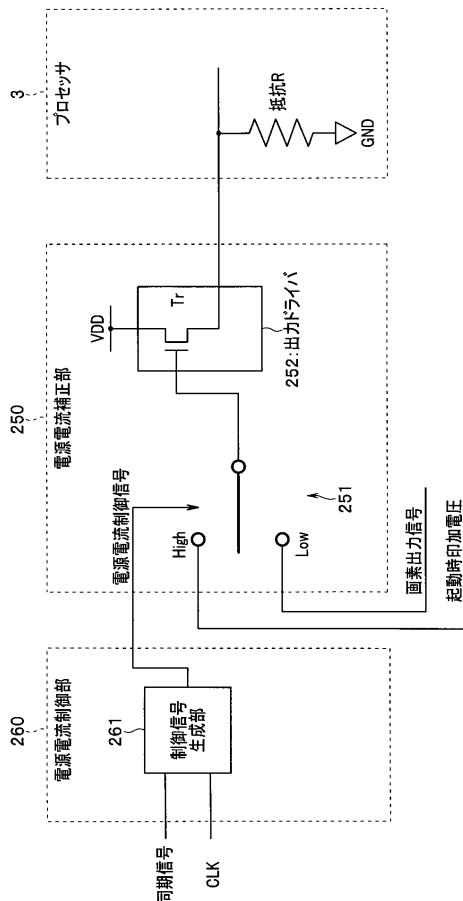

【図3】図3は、第1の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

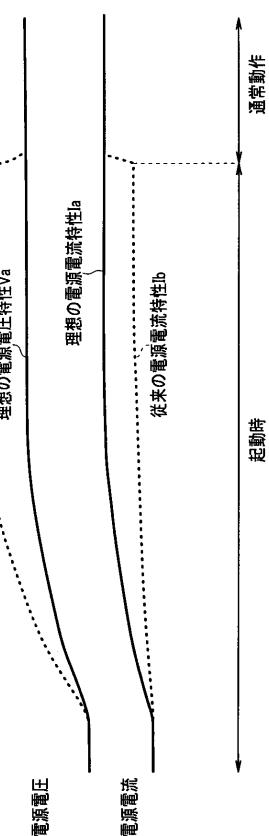

【図4】図4は、従来の内視鏡において、起動時における電源電圧特性および電源電流特

50

性、並びに、理想電源電圧特性および理想電源電流特性を示した図である。

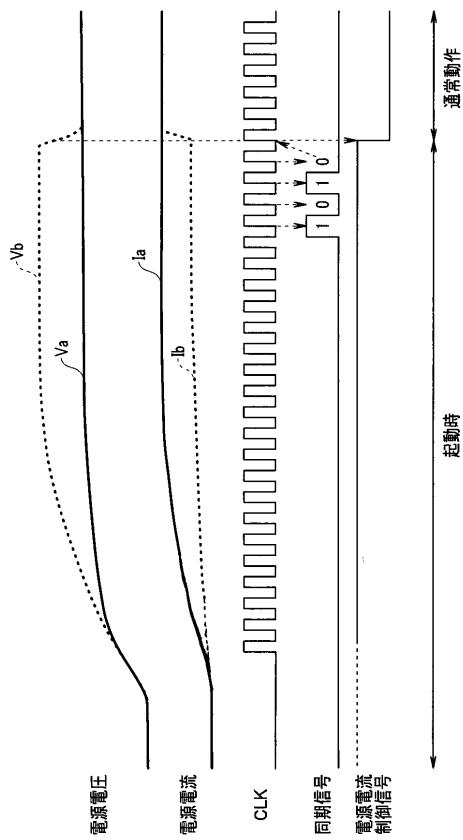

【図5】図5は、第1の実施形態の内視鏡において、起動時と通常動作時における電源電圧特性および電源電流特性、並びに、クロック信号、同期信号および電源電流制御信号の関係を示したタイミングチャートである。

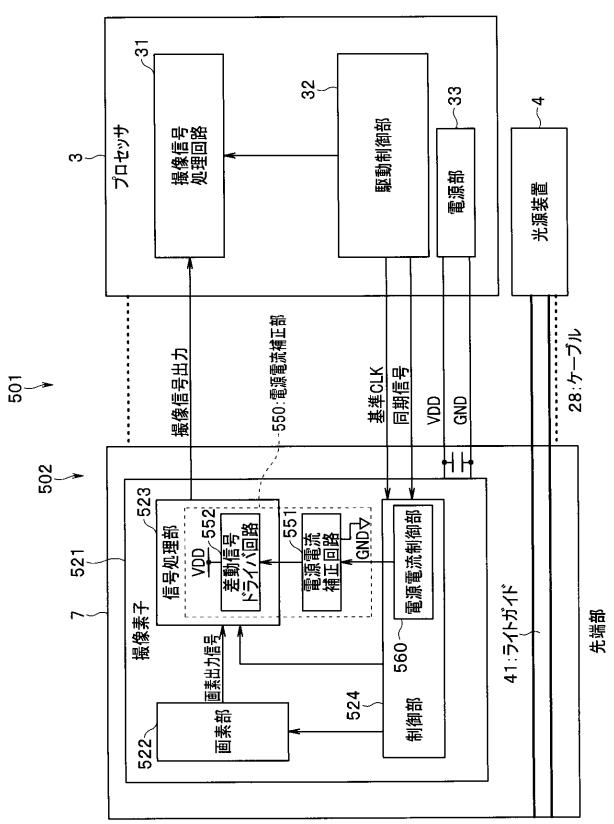

【図6】図6は、本発明の第2の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

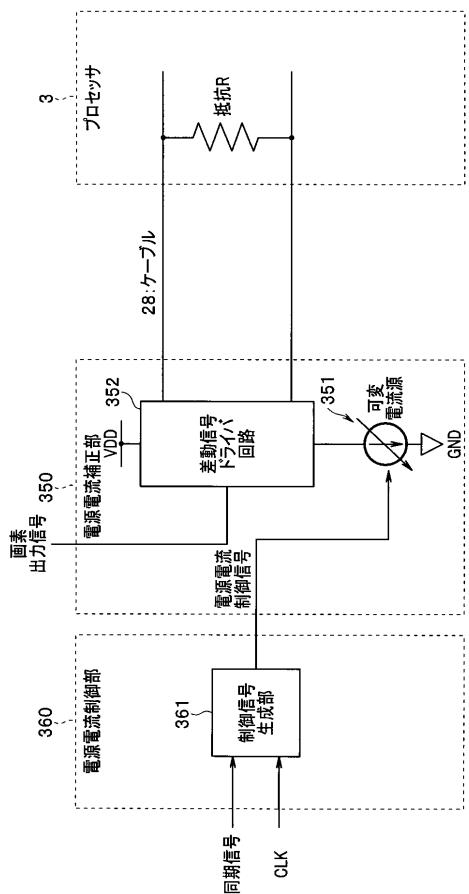

【図7】図7は、第2の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

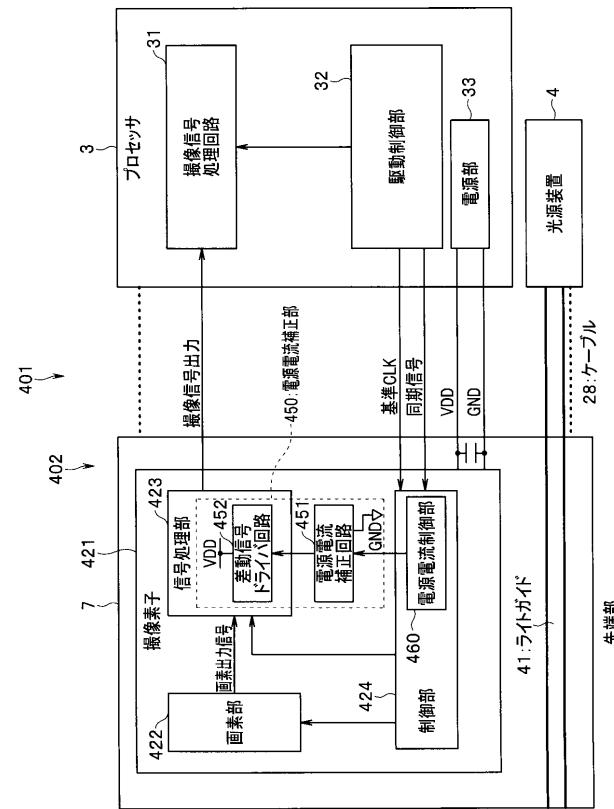

【図8】図8は、本発明の第3の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

【図9】図9は、第3の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

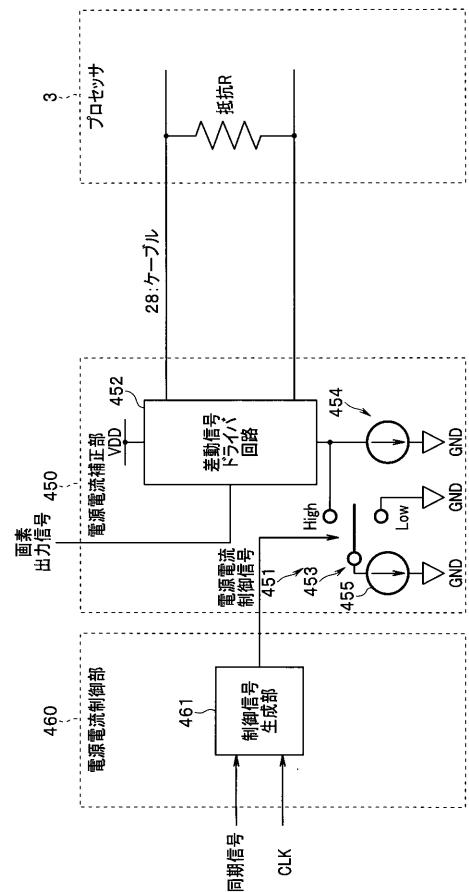

【図10】図10は、本発明の第4の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

【図11】図11は、第4の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

【図12】図12は、本発明の第5の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

【図13】図13は、第5の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

#### 【発明を実施するための形態】

##### 【0018】

以下、図面を参照して本発明の実施形態を説明する。

##### 【0019】

<第1の実施形態>

図1は、本発明の第1の実施形態の内視鏡を含む内視鏡システムの構成を示す図であり、図2は、第1の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

##### 【0020】

図1、図2に示すように、本第1の実施形態の内視鏡を有する内視鏡システム1は、被検体を観察し撮像する内視鏡2と、当該内視鏡2に接続され前記撮像信号を入力し所定の画像処理を施すビデオプロセッサ3と、被検体を照明するための照明光を供給する光源装置4と、撮像信号に応じた観察画像を表示するモニタ装置5と、を有している。

##### 【0021】

内視鏡2は、被検体の体腔内等に挿入される細長の挿入部6と、挿入部6の基端側に配設され術者が把持して操作を行う内視鏡操作部10と、内視鏡操作部10の側部から延出するように一方の端部が設けられたユニバーサルコード11と、を有して構成されている。

##### 【0022】

挿入部6は、先端側に設けられた硬質の先端部7と、先端部7の後端に設けられた湾曲自在の湾曲部8と、湾曲部8の後端に設けられた長尺かつ可撓性を有する可撓管部9と、を有して構成されている。

##### 【0023】

前記ユニバーサルコード11の基端側にはコネクタ12が設けられ、当該コネクタ12は光源装置4に接続されるようになっている。すなわち、コネクタ12の先端から突出する流体管路の接続端部となる口金(図示せず)と、照明光の供給端部となるライトガイド口金(図示せず)とは光源装置4に着脱自在で接続されるようになっている。

##### 【0024】

さらに、前記コネクタ12の側面に設けた電気接点部には接続ケーブル13の一端が接続されるようになっている。そして、この接続ケーブル13には、例えば内視鏡2におけ

10

20

30

40

50

る撮像素子（C M O Sイメージセンサ）121（図2参照）からの撮像信号を伝送する信号線、並びに、撮像素子を駆動するための制御信号線および電源線が内設され、また、他端のコネクタ部はビデオプロセッサ3に接続されるようになっている。

【0025】

図2に示すように、本実施形態の内視鏡2は、挿入部6の先端部7に配設された、被写体像を入光するレンズを含む対物光学系（図示せず）と、対物光学系における結像面に配設された撮像素子（C M O Sイメージセンサ）121と、を備える。

【0026】

また内視鏡2は、撮像素子121から延出され、当該撮像素子121から挿入部6、操作部10、ユニバーサルコード11を経て、コネクタ12に至るまで配設されたケーブル28を備える。

10

【0027】

撮像素子121は、上述したように本実施形態においてはC M O Sイメージセンサにより構成される撮像素子である。また、撮像素子121は、被写体像を入光し光電変換した後に所定の画素出力信号を出力する画素部122と、前記画素出力信号を入力し所定の信号処理を行った後、撮像信号として出力する信号処理部123と、これら画素部122、信号処理部123等を制御する制御部124と、を備える。

【0028】

ケーブル28は、各種駆動信号（基準クロックC L K、各種同期信号等）を伝送する駆動信号ライン、撮像素子121を駆動するための電源電圧V D Dを供給するための電源供給ライン、前記撮像信号を伝送する撮像信号ライン等を内包するケーブルであり、本実施形態においては、撮像素子121からコネクタ12に至るまで配設されている。

20

【0029】

前記駆動信号ラインは、ビデオプロセッサ3における駆動制御部32と撮像素子121とに接続され、撮像素子121を制御するための各種駆動信号（基準クロックC L K、各種同期信号等）を伝送する。

30

【0030】

前記電源供給ラインは、ビデオプロセッサ3における電源部33に接続され、撮像素子121に対して電源電圧を供給するためのV D Dラインおよびグランドライン（G N D）を有する。

【0031】

なお、前記V D Dライン（電源供給線）は、撮像素子121に接続された後、当該撮像素子121内部に配線され、当該撮像素子121に対して所定の電源電圧V D Dを供給する役目を果たす。

【0032】

また、撮像素子121は、電源供給線（V D Dライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部150と、所定のタイミングにおいて前記電源電流補正部150に対して制御信号を出力する電源電流制御部160と、を具備するが、詳細については後述する。

40

【0033】

一方、本実施形態の内視鏡システム1は、当該内視鏡2に接続され前記撮像信号を入力し所定の画像処理を施すビデオプロセッサ3を備える。

【0034】

本実施形態においてビデオプロセッサ3は、内視鏡2からの撮像信号を入力し、所定の画像処理を施す撮像信号処理回路31と、内視鏡2に対して各種動作制御信号を送出する駆動制御部32と、ビデオプロセッサ3内の各種回路に供給する電源電圧および内視鏡2における各種電源部に対して供給するための電源電圧を生成する電源部33と、を備える。

50

【0035】

具体的に駆動制御部32は、所定の制御信号、例えば、基準クロックC L Kおよび同期

50

信号を生成し、前記ケーブル 28 を介して撮像素子 121 に対して供給するようになっている。

【0036】

また、電源部 33 は、撮像素子 121 に供給するための電源電圧 VDD を生成し、ケーブル 28 に配した電源供給線 (VDD ライン) およびグランドライン (GND) を介して当該電源電圧 VDD を撮像素子 121 に供給するようになっている。

【0037】

次に、本第 1 の実施形態を特徴付ける、撮像素子 121 に設けた電源電流補正部 150 および電源電流制御部 160 について説明するに先立って、本発明における「撮像素子の起動時」について説明する。

10

【0038】

上述したように、本発明は、「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することを可能とした内視鏡を提供することを目的とするものであるが、本実施形態において「撮像素子の起動時」について以下、定義づける。

【0039】

<本実施形態における「撮像素子の起動時」について>

本実施形態において「撮像素子の起動時」とは、内視鏡 2 に対する電源投入時であって撮像素子 121 に対して実際に電源電圧 VDD が供給され起動が開始された直後からの極短時間を指す。

20

【0040】

より具体的に「撮像素子の起動時」とは、撮像素子 121 に電源電圧 VDD が供給され起動が開始された直後から、ビデオプロセッサ 3 における駆動制御部 32 から撮像素子 121 に対して「同期信号」が送出され、当該撮像素子 121 の電源電流制御部 160 において当該「同期信号」の最初期における信号を受信するまでの期間をいう。

【0041】

対して「撮像素子の通常動作時」とは、上述した「起動時」を経て、現に撮像素子 121 から所定の撮像信号の出力が開始された後の期間であり、撮像素子 121 自体の動作も安定し、当該撮像素子 121 に供給する電源供給線 (VDD ライン) における消費電流も定格動作の範囲内に収まっている状態の時をいう。

30

【0042】

以下、図 4 を参照して、「撮像素子の起動時」と「撮像素子の通常動作時」とにおける電源供給線 (VDD ライン) の電源電圧および電源電流の状態について説明する。

【0043】

図 4 は、従来の内視鏡において、起動時における電源電圧特性および電源電流特性、並びに、理想電源電圧特性および理想電源電流特性を示した図である。

40

【0044】

近年、内視鏡の撮像素子および挿入部等の小型化・細径化に伴って、撮像素子に電源電圧を供給する電源ケーブルについても細径化が求められ、当該ケーブル自体の抵抗値についても増大を余儀なくされていることは上述した。

【0045】

このような状況下において、上述の如き定義する「撮像素子の起動時」においては、本実施形態の如き CMOS イメージセンサ等の撮像素子は動作が安定していないことから、消費電流が通常動作時よりも少なく、例えば、数 mA (ex. 4 mA) 程度まで減少する場合があることについても先に述べたとおりである。

【0046】

具体的に、図 4 に示すように、近年における従来の内視鏡においては、「撮像素子の起動時」において撮像素子に供給される電源供給線 (VDD ライン) においては、本来であれば図 4 において符号 “Ia” にて示す「理想電源電流特性」の如き起動直後からなだらかに立ち上がるべき電流特性が、符号 “Ib” にて示す「従来の電源電流特性」の如く、

50

通常動作時に比べて無視できない程度まで落ち込む虞があった。

【0047】

このように「撮像素子の起動時」においては、上述したように電源供給線（VDDライン）において内視鏡として予定する消費電流（通常動作時を基準とする消費電流）より小さい電流しか流れない虞もあり、この場合、撮像素子には、定格（例えば3.3V）より高い電圧値、例えば、3.85V程度の電圧が印加される虞があり、撮像素子の耐圧をオーバーしてしまうという問題が生じる。

【0048】

この点を図4を用いて具体的に説明すると、「撮像素子の起動時」において撮像素子に供給される電源供給線（VDDライン）においては、図4において符号“Va”にて示す「理想電源電圧特性」の如き特性が望ましいところ、同図符号“Vb”にて示す「従来の電源電圧特性」の如く、通常動作時に比べて無視できない程度まで撮像素子に印加される電圧が増大する虞があった。

10

【0049】

本出願人はこのような事情に鑑みて、上述の如く「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することを可能とした内視鏡を提供するものであり、以下その具体的な解決方法について説明する。

【0050】

〈電源電流補正部および電源電流制御部〉

20

上述したように、撮像素子121は、電源電流補正部150および電源電流制御部160を備えることを特徴とする。以下、第1の実施形態の内視鏡2における電源電流補正部150および電源電流制御部160の構成について、図2に加え図3および図5を参照して詳しく説明する。

【0051】

図3は、第1の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図であり、図5は、第1の実施形態の内視鏡において、起動時と通常動作時における電源電圧特性および電源電流特性、並びに、クロック信号、同期信号および電源電流制御信号の関係を示したタイミングチャートである。

30

【0052】

図2、図3に示すように、本第1の実施形態の撮像素子121は、上述したように電源電流補正部150および電源電流制御部160を備える。

【0053】

電源電流補正部150は、撮像素子121に供給される電源供給線（VDDライン）とグランド（GND）との間に設けられた電源電流補正回路151を備える。この電源電流補正回路151は、直列に接続されたトランジスタ152と抵抗153とで構成され、これら直列回路が前記VDDとGNDとの間に挿入されるように配置される。

30

【0054】

また、電源電流制御部160は、撮像素子の起動時（「撮像素子の起動時」の定義については後に詳述する）において所定の制御信号（電源電流制御信号）を生成し出力する。また、その出力はビデオプロセッサ3における駆動制御部32から入力した同期信号および基準クロックCLKに応じて制御されるようになっている。

40

【0055】

また、電源電流制御部160から出力される当該制御信号（電源電流制御信号）は、電源電流補正部150における前記トランジスタ52のゲートに印加され、当該トランジスタ152をオンオフ制御するようになっている。

【0056】

ここで、電源電流補正部150は、電源電流制御部160から供給される所定の制御信号（前記電源電流制御信号）に応じて前記電源供給線（VDDライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する役目を果たす。

50

## 【0057】

一方、電源電流制御部160は、当該撮像素子121の起動時において電源供給線(VDDライン)に流れる電流を、撮像素子121の通常動作時において電源供給線(VDDライン)に流れる電流に対して相対的に増加させるための制御信号(前記電源電流制御信号)を生成し、所定のタイミングにおいて前記電源電流補正部150に対して当該制御信号を出力する役目を果たす。

## 【0058】

<本実施形態における「撮像素子の起動時」の作用>

上述の如き構成をなす電源電流補正部150および電源電流制御部160の作用について図5を参照して説明する。

10

## 【0059】

内視鏡2およびビデオプロセッサ3に対して電源が投入されると、まず、電源供給線(VDDライン)には、電源部33からの電源電圧VDDが供給され始め、その後、ビデオプロセッサ3における駆動制御部32から基準クロックCLKが送出される。

## 【0060】

このとき、電源供給線(VDDライン)に印加される電源電圧および流れる電流共に徐々に立ち上がる。

## 【0061】

一方で、電源電流制御部160からは、VDDの立ち上がりから間もなく所定電圧値に達すると“Hレベル”的制御信号(電源電流制御信号)が出力され、電源電流補正回路151におけるトランジスタ152のゲートに印加される。

20

## 【0062】

電源電流補正回路151におけるトランジスタ152は、前記“Hレベル”的制御信号(電源電流制御信号)が印加されるとオンして、VDDとGND間に所定の補正電流が流れることになる。

## 【0063】

すなわち、前記トランジスタ152がオンした際、前記抵抗153の抵抗値をR、当該トランジスタ152におけるON抵抗の値をR<sub>tr</sub>とすると、R+R<sub>tr</sub>の抵抗値に応じた補正電流が電源供給線(VDDライン)に供給されることとなる。

30

## 【0064】

このR+R<sub>tr</sub>の抵抗値は、本実施形態においては、撮像素子の起動時の消費電流と通常動作時の消費電流とがほぼ同等となるような値に設定されるようになっている。

## 【0065】

このように、電源電流補正回路151におけるトランジスタ152がオンされると、撮像素子121に供給される電源供給線(VDDライン)の電流値の立ち上がり特性カーブ(Ia)が、トランジスタ152がオフのままであると仮定した場合の特性カーブ(Ib)に比して適正な上昇変化を辿るよう補正されることとなる。

## 【0066】

また、この電流値の適正な上昇変化に伴って、電源供給線(VDDライン)の電圧値の特性カーブ(Va)についても、トランジスタ152がオフのままであると仮定した場合の特性カーブ(Vb)に比して適正な変化を辿るよう補正されることとなり、撮像素子121に対して定格を超える電圧が印加されることを防止することができる。

40

## 【0067】

この後、ビデオプロセッサ3における駆動制御部32から同期信号が送出されると、電源電流制御部160において当該同期信号のパルスを検知し、所定のパルス数を検出した後、基準クロックCLKのタイミングに基づいて電源電流補正部150に向けて出力する制御信号(電源電流制御信号)を“Lレベル”に変化させる。

## 【0068】

そして、この制御信号(電源電流制御信号)の“Lレベル”への立ち下りにより、電源電流補正回路151におけるトランジスタ152はオフされ、これにより電源供給線(V

50

DD ライン ) に対する補正電流の供給も停止する。

【 0 0 6 9 】

電源供給線 ( VDD ライン ) に対する上記補正電流供給の停止に伴い、撮像素子 121 は通常動作に移行し、画素部 122 から出力される画素出力信号に応じて信号処理部 123 から所定の撮像信号が出力されることとなる。

【 0 0 7 0 】

以上説明したように、本第 1 の実施形態によると、上述の如く「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することを可能とした内視鏡を提供することができる。

【 0 0 7 1 】

< 第 2 の実施形態 >

次に、本発明の第 2 の実施形態について説明する。

【 0 0 7 2 】

図 6 は、本発明の第 2 の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図であり、図 7 は、第 2 の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

【 0 0 7 3 】

本第 2 の実施形態の内視鏡は、その基本的な構成は第 1 の実施形態と同様であり、主に電源供給線 ( VDD ライン ) に流れる電流を変化させるように電源供給線の負荷を補正する電源電流補正部、および、所定のタイミングにおいて前記電源電流補正部に対して制御信号を出力する電源電流制御部の構成、特に電源電流補正部の構成を異にする。その他の構成は第 1 の実施形態と同様であるので、ここでは第 1 の実施形態との差異のみの説明にとどめ、共通する部分の説明については省略する。

【 0 0 7 4 】

図 6 に示すように、第 2 の実施形態の内視鏡 202 を含む内視鏡システム 201 においても、内視鏡 202 における挿入部先端部には、被写体像を入光するレンズを含む対物光学系 ( 図示せず ) と、当該対物光学系における結像面に配置された撮像素子 221 と、が配設される。

【 0 0 7 5 】

当該撮像素子 221 は、本第 2 の実施形態においても CMOS イメージセンサにより構成される撮像素子であって、被写体像を入光し光電変換した後に所定の画素出力信号を出力する画素部 222 と、前記画素出力信号を入力し所定の信号処理を行った後、撮像信号として出力する信号処理部 223 と、これら画素部 222 、信号処理部 223 等を制御する制御部 224 と、を備える。

【 0 0 7 6 】

さらに内視鏡 202 には、第 1 の実施形態における内視鏡 2 と同様に、撮像素子 221 から延出され、当該撮像素子 221 から挿入部 6 、操作部 10 、ユニバーサルコード 11 を経て、コネクタ 12 に至るまで延設されたケーブル 28 が配設されている。

【 0 0 7 7 】

ケーブル 28 は、各種駆動信号 ( 基準クロック CLK 、各種同期信号等 ) を伝送する駆動信号ライン、撮像素子 221 を駆動するための電源電圧 VDD を供給するための電源供給ライン、前記撮像信号を伝送する撮像信号ライン等を内包するケーブルである。

【 0 0 7 8 】

前記駆動信号ラインは、ビデオプロセッサ 3 における駆動制御部 32 と撮像素子 221 とに接続され、駆動制御部 32 から出力された、撮像素子 221 を制御するための各種駆動信号 ( 基準クロック CLK 、各種同期信号等 ) を伝送する。

【 0 0 7 9 】

前記電源供給ラインは、ビデオプロセッサ 3 における電源部 33 に接続され、撮像素子 221 に対して電源電圧を供給するための VDD ラインおよびグランドライン ( GND ) を有する。

10

20

30

40

50

## 【0080】

なお、本第2の実施形態においても前記VDDライン（電源供給線）は、撮像素子221に接続された後、当該撮像素子221内部に配線され、当該撮像素子221に対して所定の電源電圧VDDを供給する役目を果たす。

## 【0081】

本第2の実施形態において撮像素子221は、電源供給線（VDDライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部250と、所定のタイミングにおいて前記電源電流補正部250に対して制御信号を出力する電源電流制御部260と、を具備する。

## 【0082】

10

<第2の実施形態における電源電流補正部および電源電流制御部>

次に、撮像素子221に設けた電源電流補正部250および電源電流制御部260について図6および図7を参照して説明する。

## 【0083】

本第2の実施形態において電源電流補正部250は、図6に示すように前記信号処理部223内に設けられた出力ドライバ回路252と、当該信号処理部223外に設けられ、電源電流制御部260から出力される制御信号（電源電流制御信号）に制御され前記出力ドライバ回路252における電源電流値を補正するための電源電流補正回路251と、により構成される。

## 【0084】

20

前記出力ドライバ回路252は、前記画素部222から出力される画素出力信号を受けて後段に向けて出力する、CMOSイメージセンサにおいて通常設けられる出力ドライバーであって所定の出力トランジスタにより構成され、前記信号処理部223内において電源供給線（VDDライン）とグランド（GND）との間に設けられる。

## 【0085】

前記電源電流補正回路251は、画素部222からの画素出力信号の入力端子（図7において“Low端子”）と、当該撮像素子の起動時にのみ印加される電圧信号（起動時印加電圧）の入力端子（図7において“High端子”）とを備え、これら入力端子を前記電源電流制御部260からの電源電流制御信号に応じて切り換えて、上記いずれか一方の信号を前記出力ドライバ回路252に供給するようになっている。

30

## 【0086】

一方、電源電流制御部260は、制御部224内に設けられ、上述した電源電流補正部250に対して所定の制御信号（電源電流制御信号）を生成し送出する制御信号生成部261を備える。

## 【0087】

この制御信号生成部261は、撮像素子221の起動時（「撮像素子の起動時」の定義については上述のとおりである）において所定の制御信号（電源電流制御信号）を生成し出力する。また、その出力はビデオプロセッサ3における駆動制御部32から入力した同期信号および基準クロックCLKに応じて制御されるようになっている。

## 【0088】

40

また、電源電流制御部260から出力される当該制御信号（電源電流制御信号）は、上述したように、電源電流補正部250における電源電流補正回路251における入力端子の切り換え部を制御するようになっており、すなわち、画素部222からの画素出力信号の入力端子（Low端子）と、撮像素子の起動時にのみ印加される起動時印加電圧の入力端子（High端子）とを備え、これらいずれか一方の信号を出力ドライバ回路252における出力トランジスタのゲートに供給するようになっている。

## 【0089】

なお、この「起動時印加電圧」は、本実施形態においては、出力ドライバ回路252において撮像素子の起動時における電源電流（消費電流）と、通常動作時における電源電流（消費電流）とがほぼ同等となるような電圧値に設定されるようになっている。

50

## 【0090】

ここで、電源電流補正部250は、電源電流制御部260から供給される所定の制御信号（前記電源電流制御信号）に応じて前記電源供給線（VDDライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する役目を果たす。

## 【0091】

一方、電源電流制御部260は、当該撮像素子221の起動時において電源供給線（VDDライン）に流れる電流を、撮像素子221の通常動作時において電源供給線（VDDライン）に流れる電流に対して相対的に増加させるための制御信号（前記電源電流制御信号）を生成し、所定のタイミングにおいて前記電源電流補正部250に対して当該制御信号を出力する役目を果たす。

10

## 【0092】

<本第2の実施形態における「撮像素子の起動時」の作用>

上述の如き構成をなす電源電流補正部250および電源電流制御部260の作用について上述した図5を参照して説明する。

## 【0093】

第1の実施形態と同様に、内視鏡2およびビデオプロセッサ3に対して電源が投入されると、電源供給線（VDDライン）に印加される電源電圧および流れる電流共に徐々に立ち上がる。

## 【0094】

一方で、電源電流制御部260における制御信号生成部261において、VDDの立ち上がりから間もなく所定電圧値に達すると“Hレベル”の制御信号（電源電流制御信号）が生成され、電源電流補正回路251に向けて出力される。

20

## 【0095】

電源電流補正回路251においては、当該“Hレベル”の電源電流制御信号に応じて、High端子側が選択され、すなわち、「起動時印加電圧」が選択され当該電圧が出力ドライバ回路252における出力トランジスタのゲートに印加される。これにより出力ドライバ回路252は、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるように制御される。

## 【0096】

このように、本第2の実施形態においても、電源電流補正回路251において「起動時印加電圧」が選択され当該電圧が出力ドライバ回路252における出力トランジスタのゲートに印加されると、撮像素子221に供給される電源供給線（VDDライン）の電流値の立ち上がり特性カーブ（Ia）は、当該出力トランジスタのゲートに当該電圧が印加されないと仮定した特性カーブ（Ib）に比して適正な上昇変化を辿るよう補正されることとなる（図5参照）。

30

## 【0097】

また、この電流値の適正な上昇変化に伴って、電源供給線（VDDライン）の電圧値の特性カーブ（Va）についても、特性カーブ（Vb）に比して適正な変化を辿るよう補正されることとなり、撮像素子221に対して定格を超える電圧が印加されることを防止することができる（図5参照）。

40

## 【0098】

この後、ビデオプロセッサ3における駆動制御部32から同期信号が送出されると、電源電流制御部260において当該同期信号のパルスを検知し、所定のパルス数を検出した後、基準クロックCLKのタイミングに基づいて電源電流補正部250に向けて出力する制御信号（電源電流制御信号）を“Lレベル”に変化させる。

## 【0099】

そして、この制御信号（電源電流制御信号）の“Lレベル”への立ち下りにより、電源電流補正回路251においてLow端子側が選択され、すなわち、画素部222からの「画素出力信号」が選択され、当該出力信号が出力ドライバ回路252における出力トランジスタのゲートに印加される。これにより出力ドライバ回路252は、通常動作時に係る

50

動作に移行し、画素部 222 から出力される画素出力信号に応じて所定の撮像信号を出力することとなる。

【0100】

以上説明したように、本第2の実施形態によつても、上述の如く「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することができる。

【0101】

<第3の実施形態>

次に、本発明の第3の実施形態について説明する。

【0102】

図8は、本発明の第3の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図であり、図9は、第3の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

10

【0103】

本第3の実施形態の内視鏡は、その基本的な構成は第1の実施形態と同様であり、主に電源供給線(VDDライン)に流れる電流を変化させるように電源供給線の負荷を補正する電源電流補正部、および、所定のタイミングにおいて前記電源電流補正部に対して制御信号を出力する電源電流制御部の構成、特に電源電流補正部の構成を異にする。その他の構成は第1の実施形態と同様であるので、ここでは第1の実施形態との差異のみの説明にとどめ、共通する部分の説明については省略する。

20

【0104】

図8に示すように、第3の実施形態の内視鏡302を含む内視鏡システム301においても、内視鏡302における挿入部先端部には、被写体像を入光するレンズを含む対物光学系(図示せず)と、当該対物光学系における結像面に配置された撮像素子321と、が配設される。

【0105】

当該撮像素子321は、本第3の実施形態においてもCMOSイメージセンサにより構成される撮像素子であつて、被写体像を入光し光電変換した後に所定の画素出力信号を出力する画素部322と、前記画素出力信号を入力し所定の信号処理を行つた後、撮像信号として出力する信号処理部323と、これら画素部322、信号処理部323等を制御する制御部324と、を備える。

30

【0106】

さらに内視鏡302には、第1の実施形態における内視鏡2と同様に、撮像素子321から延出され、当該撮像素子321から挿入部6、操作部10、ユニバーサルコード11を経て、コネクタ12に至るまで延設されたケーブル28が配設されている。

【0107】

ケーブル28は、各種駆動信号(基準クロックCLK、各種同期信号等)を伝送する駆動信号ライン、撮像素子321を駆動するための電源電圧VDDを供給するための電源供給ライン、前記撮像信号を伝送する撮像信号ライン等を内包するケーブルである。

40

【0108】

前記駆動信号ラインは、ビデオプロセッサ3における駆動制御部32と撮像素子321とに接続され、駆動制御部32から出力された、撮像素子321を制御するための各種駆動信号(基準クロックCLK、各種同期信号等)を伝送する。

【0109】

前記電源供給ラインは、ビデオプロセッサ3における電源部33に接続され、撮像素子321に対して電源電圧を供給するためのVDDラインおよびグランドライン(GND)を有する。

【0110】

なお、本第3の実施形態においても前記VDDライン(電源供給線)は、撮像素子321に接続された後、当該撮像素子321内部に配線され、当該撮像素子321に対して所

50

定の電源電圧 V D D を供給する役目を果たす。

【 0 1 1 1 】

本第 3 の実施形態において撮像素子 3 2 1 は、電源供給線 ( V D D ライン ) に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部 3 5 0 と、所定のタイミングにおいて前記電源電流補正部 3 5 0 に対して制御信号を出力する電源電流制御部 3 6 0 と、を具備する。

【 0 1 1 2 】

< 第 3 の実施形態における電源電流補正部および電源電流制御部 >

次に、撮像素子 3 2 1 に設けた電源電流補正部 3 5 0 および電源電流制御部 3 6 0 について図 8 および図 9 を参照して説明する。

10

【 0 1 1 3 】

本第 3 の実施形態において電源電流補正部 3 5 0 は、図 8 に示すように前記信号処理部 3 2 3 内に設けられた差動信号ドライバ回路 3 5 2 と、当該差動信号ドライバ回路 3 5 2 外に設けられ、電源電流制御部 3 6 0 から出力される制御信号 ( 電源電流制御信号 ) に制御され前記差動信号ドライバ回路 3 5 2 における電源電流値を補正するための電源電流補正回路 3 5 1 と、により構成される。

【 0 1 1 4 】

差動信号ドライバ回路 3 5 2 は、前記画素部 3 2 2 から出力される画素出力信号を入力し所定の差動信号である撮像信号を後段に向けて出力するドライバーであって、前記信号処理部 3 2 3 内において電源供給線 ( V D D ライン ) とグランド ( G N D ) との間に設けられる。

20

【 0 1 1 5 】

また、電源電流補正回路 3 5 1 は、当該差動出力ドライバ回路 3 5 2 の駆動電流を変化させる可変電流源により構成され、電源供給線 ( V D D ライン ) とグランド ( G N D ) との間ににおいて前記差動信号ドライバ回路 3 5 2 に対して直列に接続され、当該差動出力ドライバ回路 3 5 2 の駆動電流を切り換え可能とする補正回路としての役目を果たす。

【 0 1 1 6 】

一方、電源電流制御部 3 6 0 は、制御部 3 2 4 内に設けられ、上述した電源電流補正部 3 5 0 に対して所定の制御信号 ( 電源電流制御信号 ) を生成し送出する制御信号生成部 3 6 1 を備える。

30

【 0 1 1 7 】

この制御信号生成部 3 6 1 は、撮像素子 3 2 1 の起動時 ( 「撮像素子の起動時」の定義については上述のとおりである ) において所定の制御信号 ( 電源電流制御信号 ) を生成し出力する。また、その出力はビデオプロセッサ 3 における駆動制御部 3 2 から入力した同期信号および基準クロック C L K に応じて制御されるようになっている。

【 0 1 1 8 】

また、電源電流制御部 3 6 0 から出力される当該制御信号 ( 電源電流制御信号 ) は、上述したように、電源電流補正部 3 5 0 における電源電流補正回路 3 5 1 ( 以下、可変電流源 3 5 1 ともいう ) を制御するようになっている。

【 0 1 1 9 】

すなわち、この「可変電流源 3 5 1 」は、上記電源電流制御部 3 6 0 から出力される電源電流制御信号に応じてその「電流値」が切り換えられるようになっており、差動信号ドライバ回路 3 5 2 において撮像素子の起動時における電源電流 ( 消費電流 ) と、通常動作時における電源電流 ( 消費電流 ) とがほぼ同等となるように、「撮像素子の起動時」における「起動時用の電流値」が設定されるようになっている。

40

【 0 1 2 0 】

具体的に可変電流源 3 5 1 は、「撮像素子の起動時」においては、相対的に差動信号ドライバ回路 3 5 2 の駆動電流が増すことにより、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるような「起動時用の電流値」に切り換わるように制御される。

50

## 【0121】

ここで、電源電流補正部350は、電源電流制御部360から供給される所定の制御信号（前記電源電流制御信号）に応じて前記電源供給線（VDDライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する役目を果たす。

## 【0122】

一方、電源電流制御部360は、当該撮像素子321の起動時において電源供給線（VDDライン）に流れる電流を、撮像素子321の通常動作時において電源供給線（VDDライン）に流れる電流に対して相対的に増加させるための制御信号（前記電源電流制御信号）を生成し、所定のタイミングにおいて前記電源電流補正部350に対して当該制御信号を出力する役目を果たす。

10

## 【0123】

〈本第3の実施形態における「撮像素子の起動時」の作用〉

上述の如き構成をなす電源電流補正部350および電源電流制御部360の作用について上述した図5を参照して説明する。

## 【0124】

第1の実施形態と同様に、内視鏡2およびビデオプロセッサ3に対して電源が投入されると、電源供給線（VDDライン）に印加される電源電圧および流れる電流共に徐々に立ち上がる。

20

## 【0125】

一方で、電源電流制御部360における制御信号生成部361において、VDDの立ち上がりから間もなく所定電圧値に達すると“Hレベル”の制御信号（電源電流制御信号）が生成され、電源電流補正回路（可変電流源）351に向けて出力される。

## 【0126】

前記可変電流源351においては、当該“Hレベル”の電源電流制御信号に応じて、相対的に差動信号ドライバ回路352の駆動電流が増すような電流値に切り換わり、これにより差動信号ドライバ回路352は、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるように制御される。

30

## 【0127】

このように、本第3の実施形態においても、電源電流補正回路（可変電流源）351が「起動時用の電流値」に切り換えられると、撮像素子321に供給される電源供給線（VDDライン）の電流値の立ち上がり特性カーブ（Ia）は、当該可変電流源351が「起動時用の電流値」に切り換えられない仮定した特性カーブ（Ib）に比して適正な上昇変化を辿るよう補正されることとなる（図5参照）。

## 【0128】

また、この電流値の適正な上昇変化に伴って、電源供給線（VDDライン）の電圧値の特性カーブ（Va）についても、特性カーブ（Vb）に比して適正な変化を辿るよう補正されることとなり、撮像素子321に対して定格を超える電圧が印加されることを防止することができる（図5参照）。

40

## 【0129】

この後、ビデオプロセッサ3における駆動制御部32から同期信号が送出されると、電源電流制御部360において当該同期信号のパルスを検知し、所定のパルス数を検出した後、基準クロックCLKのタイミングに基づいて電源電流補正部350に向けて出力する制御信号（電源電流制御信号）を“Lレベル”に変化させる。

## 【0130】

そして、この制御信号（電源電流制御信号）の“Lレベル”への立ち下りにより、電源電流補正回路（可変電流源）351が「通常動作用の電流値」に切り換えられると、差動信号ドライバ回路352は通常動作時に係る動作に移行し、画素部322から出力される画素出力信号に応じて所定の撮像信号を出力することとなる。

## 【0131】

以上説明したように、本第3の実施形態によっても、上述の如く「撮像素子の起動時」

50

等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することができる。

【0132】

<第4の実施形態>

次に、本発明の第4の実施形態について説明する。

【0133】

図10は、本発明の第4の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図であり、図11は、第4の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

【0134】

本第4の実施形態の内視鏡は、その基本的な構成は第1の実施形態と同様であり、主に電源供給線(VDDライン)に流れる電流を変化させないように電源供給線の負荷を補正する電源電流補正部、および、所定のタイミングにおいて前記電源電流補正部に対して制御信号を出力する電源電流制御部の構成、特に電源電流補正部の構成を異にする。その他の構成は第1の実施形態と同様であるので、ここでは第1の実施形態との差異のみの説明にとどめ、共通する部分の説明については省略する。

10

【0135】

図10に示すように、第4の実施形態の内視鏡402を含む内視鏡システム401においても、内視鏡402における挿入部先端部には、被写体像を入光するレンズを含む対物光学系(図示せず)と、当該対物光学系における結像面に配置された撮像素子421と、が配設される。

20

【0136】

当該撮像素子421は、本第4の実施形態においてもCMOSイメージセンサにより構成される撮像素子であって、被写体像を入光し光電変換した後に所定の画素出力信号を出力する画素部422と、前記画素出力信号を入力し所定の信号処理を行った後、撮像信号として出力する信号処理部423と、これら画素部422、信号処理部423等を制御する制御部424と、を備える。

20

【0137】

さらに内視鏡402には、第1の実施形態における内視鏡2と同様に、撮像素子421から延出され、当該撮像素子421から挿入部6、操作部10、ユニバーサルコード11を経て、コネクタ12に至るまで延設されたケーブル28が配設されている。

30

【0138】

ケーブル28は、各種駆動信号(基準クロックCLK、各種同期信号等)を伝送する駆動信号ライン、撮像素子421を駆動するための電源電圧VDDを供給するための電源供給ライン、前記撮像信号を伝送する撮像信号ライン等を内包するケーブルである。

30

【0139】

前記駆動信号ラインは、ビデオプロセッサ3における駆動制御部32と撮像素子421とに接続され、駆動制御部32から出力された、撮像素子421を制御するための各種駆動信号(基準クロックCLK、各種同期信号等)を伝送する。

40

【0140】

前記電源供給ラインは、ビデオプロセッサ3における電源部33に接続され、撮像素子421に対して電源電圧を供給するためのVDDラインおよびグランドライン(GND)を有する。

【0141】

なお、本第4の実施形態においても前記VDDライン(電源供給線)は、撮像素子421に接続された後、当該撮像素子421内部に配線され、当該撮像素子421に対して所定の電源電圧VDDを供給する役目を果たす。

【0142】

本第4の実施形態において撮像素子421は、電源供給線(VDDライン)に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部450と、所定の

50

タイミングにおいて前記電源電流補正部 450 に対して制御信号を出力する電源電流制御部 460 と、を具備する。

【0143】

<第4の実施形態における電源電流補正部および電源電流制御部>

次に、撮像素子 421 に設けた電源電流補正部 450 および電源電流制御部 460 について図 10 および図 11 を参照して説明する。

【0144】

本第4の実施形態において電源電流補正部 450 は、図 10 に示すように前記信号処理部 423 内に設けられた差動信号ドライバ回路 452 と、当該差動信号ドライバ回路 452 外に設けられ、電源電流制御部 460 から出力される制御信号（電源電流制御信号）に制御され前記差動信号ドライバ回路 452 における電源電流値を補正するための電源電流補正回路 451 と、により構成される。

10

【0145】

差動信号ドライバ回路 452 は、第3の実施形態と同様に、前記画素部 422 から出力される画素出力信号を入力し所定の差動信号である撮像信号を後段に向けて出力するドライバーであって、前記信号処理部 423 内において電源供給線（VDD ライン）とグランド（GND）との間に設けられる。

【0146】

また、電源電流補正回路 451 は、当該差動出力ドライバ回路 452 の駆動電流を設定する複数の電流源である第1の電流源 454 と第2の電流源 455 と、を有する。さらに電源電流補正回路 451 は、差動信号ドライバ回路 452 の電流源として、第1の電流源 454 と第2の電流源 455 とが並列に接続された上で、これらの並列に接続された電流源が差動信号ドライバ回路 452 と直列に接続される第1の状態（起動時の状態；“High 端子”が選択された状態）と、第1の電流源 454 のみが差動信号ドライバ回路 452 と直列に接続される第2の状態（通常動作時の状態；“Low 端子”が選択された状態）と、とを切り換える電流源選択スイッチ 453 と、をさらに有して構成される。

20

【0147】

なお、当該電源電流補正回路 451 は、上述した第1の電流源 454、または第1の電流源 454 と第2の電流源 455 の並列回路が、電源供給線（VDD ライン）とグランド（GND）との間ににおいて前記差動信号ドライバ回路 452 に対して直列に接続されることから、当該差動出力ドライバ回路 452 の駆動電流を切り換え可能とする補正回路としての役目を果たす。

30

【0148】

一方、電源電流制御部 460 は、制御部 424 内に設けられ、上述した電源電流補正部 450 に対して所定の制御信号（電源電流制御信号）を生成し送出する制御信号生成部 461 を備える。

30

【0149】

この制御信号生成部 461 は、撮像素子 421 の起動時（「撮像素子の起動時」の定義については上述のとおりである）において所定の制御信号（電源電流制御信号）を生成し出力する。また、その出力はビデオプロセッサ 3 における駆動制御部 32 から入力した同期信号および基準クロック CLK に応じて制御されるようになっている。

40

【0150】

また、電源電流制御部 460 から出力される当該制御信号（電源電流制御信号）は、上述したように、電源電流補正部 450 における電源電流補正回路 451 における上記電流源選択スイッチ 453 を制御するようになっている。

【0151】

すなわち、電源電流補正回路 451 は、上記電源電流制御部 460 から出力される電源電流制御信号に応じて、上述の如く前記差動出力ドライバ回路 452 の駆動電流を設定する電流源の種類を選択することにより、差動信号ドライバ回路 452 に流れる駆動電流の「電流値」を選択するようになっている。

50

## 【0152】

すなわち、電源電流補正回路451は、その「電流値」を切り換えるようになっており、差動信号ドライバ回路452において撮像素子の起動時における電源電流（消費電流）と、通常動作時における電源電流（消費電流）とがほぼ同等となるように、前記第1の電流源454および第2の電流源455の「電流値」が設定されるようになっている。

## 【0153】

具体的に電源電流補正回路451は、「撮像素子の起動時」においては、相対的に差動信号ドライバ回路452の駆動電流が増すことにより、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるような「起動時用の電流値」に切り換わるように制御される。

10

## 【0154】

ここで、電源電流補正部450は、電源電流制御部460から供給される所定の制御信号（前記電源電流制御信号）に応じて前記電源供給線（VDDライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する役目を果たす。

## 【0155】

一方、電源電流制御部460は、当該撮像素子421の起動時において電源供給線（VDDライン）に流れる電流を、撮像素子421の通常動作時において電源供給線（VDDライン）に流れる電流に対して相対的に増加させるための制御信号（前記電源電流制御信号）を生成し、所定のタイミングにおいて前記電源電流補正部450に対して当該制御信号を出力する役目を果たす。

20

## 【0156】

＜本第4の実施形態における「撮像素子の起動時」の作用＞

上述の如き構成をなす電源電流補正部450および電源電流制御部460の作用について上述した図5を参照して説明する。

## 【0157】

第1の実施形態と同様に、内視鏡2およびビデオプロセッサ3に対して電源が投入されると、電源供給線（VDDライン）に印加される電源電圧および流れる電流共に徐々に立ち上がる。

## 【0158】

一方で、電源電流制御部460における制御信号生成部461において、VDDの立ち上がりから間もなく所定電圧値に達すると“Hレベル”的制御信号（電源電流制御信号）が生成され、電源電流補正回路451に向けて出力される。

30

## 【0159】

前記電源電流補正回路451においては、当該“Hレベル”的電源電流制御信号に応じて電流源選択スイッチ453が切り換わり、相対的に差動信号ドライバ回路452の駆動電流が増すように第1の電流源454と第2の電流源455とが稼働する状態が選択され、これにより差動信号ドライバ回路452は、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるよう制御される。

## 【0160】

このように、本第4の実施形態においても、電源電流補正回路451が「起動時用の電流値」に切り換えられると、撮像素子421に供給される電源供給線（VDDライン）の電流値の立ち上がり特性カーブ（Ia）は、当該電源電流補正回路451が「起動時用の電流値」に切り換えられない仮定した特性カーブ（Ib）に比して適正な上昇変化を辿るよう補正されることとなる（図5参照）。

40

## 【0161】

また、この電流値の適正な上昇変化に伴って、電源供給線（VDDライン）の電圧値の特性カーブ（Va）についても、特性カーブ（Vb）に比して適正な変化を辿るよう補正されることとなり、撮像素子421に対して定格を超える電圧が印加されることを防止することができる（図5参照）。

## 【0162】

50

この後、ビデオプロセッサ3における駆動制御部32から同期信号が送出されると、電源電流制御部460において当該同期信号のパルスを検知し、所定のパルス数を検出した後、基準クロックCLKのタイミングに基づいて電源電流補正部450に向けて出力する制御信号（電源電流制御信号）を“Lレベル”に変化させる。

【0163】

そして、この制御信号（電源電流制御信号）の“Lレベル”への立ち下りにより、電源電流補正回路451が「通常動作用の電流値」に切り換えられると、差動信号ドライバ回路452は通常動作時に係る動作に移行し、画素部422から出力される画素出力信号に応じて所定の撮像信号を出力することとなる。

【0164】

以上説明したように、本第4の実施形態によっても、上述の如く「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することができる。

【0165】

<第5の実施形態>

次に、本発明の第5の実施形態について説明する。

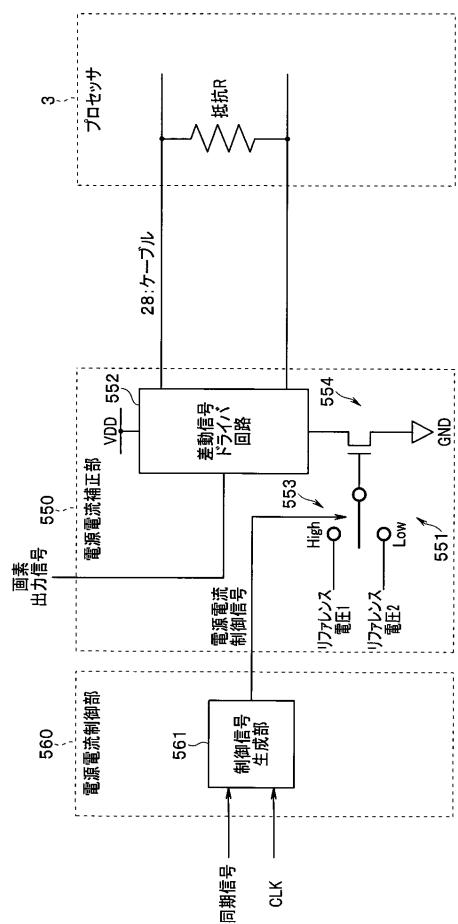

【0166】

図12は、本発明の第5の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図であり、図13は、第5の実施形態の内視鏡における電源電流補正部および電源電流制御部の構成を示すブロック図である。

10

20

【0167】

本第5の実施形態の内視鏡は、その基本的な構成は第1の実施形態と同様であり、主に電源供給線（VDDライン）に流れる電流を変化させるように電源供給線の負荷を補正する電源電流補正部、および、所定のタイミングにおいて前記電源電流補正部に対して制御信号を出力する電源電流制御部の構成、特に電源電流補正部の構成を異にする。その他の構成は第1の実施形態と同様であるので、ここでは第1の実施形態との差異のみの説明にとどめ、共通する部分の説明については省略する。

【0168】

図12に示すように、第5の実施形態の内視鏡502を含む内視鏡システム501においても、内視鏡502における挿入部先端部には、被写体像を入光するレンズを含む対物光学系（図示せず）と、当該対物光学系における結像面に配置された撮像素子521と、が配設される。

30

【0169】

当該撮像素子521は、本第5の実施形態においてもCMOSイメージセンサにより構成される撮像素子であって、被写体像を入光し光電変換した後に所定の画素出力信号を出力する画素部522と、前記画素出力信号を入力し所定の信号処理を行った後、撮像信号として出力する信号処理部523と、これら画素部522、信号処理部523等を制御する制御部524と、を備える。

【0170】

さらに内視鏡502には、第1の実施形態における内視鏡2と同様に、撮像素子521から延出され、当該撮像素子521から挿入部6、操作部10、ユニバーサルコード11を経て、コネクタ12に至るまで延設されたケーブル28が配設されている。

40

【0171】

ケーブル28は、各種駆動信号（基準クロックCLK、各種同期信号等）を伝送する駆動信号ライン、撮像素子521を駆動するための電源電圧VDDを供給するための電源供給ライン、前記撮像信号を伝送する撮像信号ライン等を内包するケーブルである。

【0172】

前記駆動信号ラインは、ビデオプロセッサ3における駆動制御部32と撮像素子521とに接続され、駆動制御部32から出力された、撮像素子521を制御するための各種駆動信号（基準クロックCLK、各種同期信号等）を伝送する。

50

## 【0173】

前記電源供給ラインは、ビデオプロセッサ3における電源部33に接続され、撮像素子521に対して電源電圧を供給するためのVDDラインおよびグランドライン(GND)を有する。

## 【0174】

なお、本第5の実施形態においても前記VDDライン(電源供給線)は、撮像素子521に接続された後、当該撮像素子521内部に配線され、当該撮像素子521に対して所定の電源電圧VDDを供給する役目を果たす。

## 【0175】

本第5の実施形態において撮像素子521は、電源供給線(VDDライン)に流れる電流を変化させるように当該電源供給線の負荷を補正する電源電流補正部550と、所定のタイミングにおいて前記電源電流補正部450に対して制御信号を出力する電源電流制御部560と、を具備する。

10

## 【0176】

<第5の実施形態における電源電流補正部および電源電流制御部>

次に、撮像素子521に設けた電源電流補正部550および電源電流制御部560について図12および図13を参照して説明する。

## 【0177】

本第5の実施形態において電源電流補正部550は、図12に示すように前記信号処理部523内に設けられた差動信号ドライバ回路552と、当該差動信号ドライバ回路552外に設けられ、電源電流制御部560から出力される制御信号(電源電流制御信号)に制御され前記差動信号ドライバ回路552における電源電流値を補正するための電源電流補正回路551と、により構成される。

20

## 【0178】

差動信号ドライバ回路552は、第3の実施形態と同様に、前記画素部522から出力される画素出力信号を入力し所定の差動信号である撮像信号を後段に向けて出力するドライバーであって、前記信号処理部523内において電源供給線(VDDライン)とグランド(GND)との間に設けられる。

## 【0179】

また、電源電流補正回路551は、当該差動出力ドライバ回路552の駆動電流を設定するトランジスタ554と、トランジスタ554に第1のリファレンス電圧が印加する第1の状態(起動時の状態;“High端子”が選択された状態)と、トランジスタ554に第2のリファレンス電圧が印加する第2の状態(通常動作時の状態;“Low端子”が選択された状態)と、とを切り換える印加電圧選択スイッチ553と、を有して構成される。

30

## 【0180】

なお、当該電源電流補正回路551は、上述したトランジスタ554が、電源供給線(VDDライン)とグランド(GND)との間ににおいて前記差動信号ドライバ回路552に対して直列に接続されることから、当該差動出力ドライバ回路552の駆動電流を切り替え可能とする補正回路としての役目を果たす。

40

## 【0181】

一方、電源電流制御部560は、制御部524内に設けられ、上述した電源電流補正部550に対して所定の制御信号(電源電流制御信号)を生成し送出する制御信号生成部561を備える。

## 【0182】

この制御信号生成部561は、撮像素子521の起動時(「撮像素子の起動時」の定義については上述のとおりである)において所定の制御信号(電源電流制御信号)を生成し出力する。また、その出力はビデオプロセッサ3における駆動制御部32から入力した同期信号および基準クロックCLKに応じて制御されるようになっている。

## 【0183】

50

また、電源電流制御部 560 から出力される当該制御信号（電源電流制御信号）は、上述したように、電源電流補正部 550 における電源電流補正回路 551 における上記印加電圧選択スイッチ 553 を制御するようになっている。

【0184】

すなわち、電源電流補正回路 551 は、上記電源電流制御部 560 から出力される電源電流制御信号に応じて、上述の如く前記トランジスタ 554 に印加するリファレンス電圧を選択することにより、差動信号ドライバ回路 552 に流れる駆動電流の「電流値」を選択するようになっている。

【0185】

すなわち、電源電流補正回路 551 は、リファレンス電圧を選択することにより「差動信号ドライバ回路 552 に流れる駆動電流の電流値」を切り換えるようになっており、差動信号ドライバ回路 552 において撮像素子の起動時における電源電流（消費電流）と、通常動作時における電源電流（消費電流）とがほぼ同等となるように、前記第 1 のリファレンス電圧と第 2 のリファレンス電圧が設定されるようになっている。

10

【0186】

具体的に電源電流補正回路 551 は、「撮像素子の起動時」においては、相対的に差動信号ドライバ回路 552 の駆動電流が増すことにより、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるような「起動時用の電流値」に切り換わるように制御される。

20

【0187】

ここで、電源電流補正部 550 は、電源電流制御部 560 から供給される所定の制御信号（前記電源電流制御信号）に応じて前記電源供給線（VDD ライン）に流れる電流を変化させるように当該電源供給線の負荷を補正する役目を果たす。

【0188】

一方、電源電流制御部 560 は、当該撮像素子 521 の起動時において電源供給線（VDD ライン）に流れる電流を、撮像素子 521 の通常動作時において電源供給線（VDD ライン）に流れる電流に対して相対的に増加させるための制御信号（前記電源電流制御信号）を生成し、所定のタイミングにおいて前記電源電流補正部 550 に対して当該制御信号を出力する役目を果たす。

30

【0189】

〈本第 5 の実施形態における「撮像素子の起動時」の作用〉

上述の如き構成をなす電源電流補正部 550 および電源電流制御部 560 の作用について上述した図 5 を参照して説明する。

【0190】

第 1 の実施形態と同様に、内視鏡 2 およびビデオプロセッサ 3 に対して電源が投入されると、電源供給線（VDD ライン）に印加される電源電圧および流れる電流共に徐々に立ち上がる。

【0191】

一方で、電源電流制御部 560 における制御信号生成部 561 において、VDD の立ち上がりから間もなく所定電圧値に達すると“H レベル”的制御信号（電源電流制御信号）が生成され、電源電流補正回路 551 に向けて出力される。

40

【0192】

前記電源電流補正回路 551 においては、当該“H レベル”的電源電流制御信号に応じて印加電圧選択スイッチ 553 が切り換わり、相対的に差動信号ドライバ回路 552 の駆動電流が増すように、トランジスタ 554 に対して第 1 のリファレンス電圧が印加される状態が選択され、これにより差動信号ドライバ回路 552 は、当該撮像素子の起動時においても、通常動作時における消費電流とほぼ同等の電流が流れるよう制御される。

【0193】

このように、本第 5 の実施形態においても、電源電流補正回路 551 が「起動時用の電流値」に切り換えられると、撮像素子 521 に供給される電源供給線（VDD ライン）の

50

電流値の立ち上がり特性カーブ (Ia) は、当該電源電流補正回路 551 が「起動時用の電流値」に切り換えられていない仮定した特性カーブ (Ib) に比して適正な上昇変化を辿るよう補正されることとなる (図 5 参照)。

【0194】

また、この電流値の適正な上昇変化に伴って、電源供給線 (VDD ライン) の電圧値の特性カーブ (Va) についても、特性カーブ (Vb) に比して適正な変化を辿るよう補正されることとなり、撮像素子 521 に対して定格を超える電圧が印加されることを防止することができる (図 5 参照)。

【0195】

この後、ビデオプロセッサ 3 における駆動制御部 32 から同期信号が送出されると、電源電流制御部 560 において当該同期信号のパルスを検知し、所定のパルス数を検出した後、基準クロック CLK のタイミングに基づいて電源電流補正部 550 に向けて出力する制御信号 (電源電流制御信号) を“L レベル”に変化させる。

10

【0196】

そして、この制御信号 (電源電流制御信号) の“L レベル”への立ち下りにより、電源電流補正回路 551 が「通常動作用の電流値」に切り換えられると、差動信号ドライバ回路 552 は通常動作時に係る動作に移行し、画素部 522 から出力される画素出力信号に応じて所定の撮像信号を出力することとなる。

【0197】

以上説明したように、本第 5 の実施形態によっても、上述の如く「撮像素子の起動時」等の動作不安定時における意図しない消費電流の低下状態を是正し、起動時と通常動作時とで消費電流を一定化することができる。

20

【0198】

本発明は、上述した実施形態に限定されるものではなく、本発明の要旨を変えない範囲において、種々の変更、改変等が可能である。

【符号の説明】

【0199】

1 … 内視鏡システム

2 … 内視鏡

7 … 先端部

30

121、221, 321, 421, 521 … 撮像素子 (CMOS イメージセンサ)

122、222, 322, 422, 522 … 画素部

123、223, 323, 423, 523 … 信号処理部

124、224, 324, 424, 524 … 制御部

28 … ケーブル

3 … ビデオプロセッサ

31 … 撮像信号処理部

32 … 駆動制御部

33 … 電源部

40

4 … 光源装置

150、250, 350, 450, 550 … 電源電流補正部

151、251, 351, 451, 551 … 電源電流補正回路

160、260, 360, 460, 560 … 電源電流制御部

252 … 出力ドライバ回路

352, 452, 552 … 差動信号ドライバ回路

261, 361, 461, 561 … 制御信号生成部

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 図 6 】

【 図 7 】

【 図 8 】

【 义 9 】

【 図 1 0 】

### 【図11】

【 図 1 2 】

【図 1 3】

---

フロントページの続き

F ターム(参考) 4C161 CC06 DD03 FF45 JJ11 LL02 SS03

|                |                                                                                                                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 内镜                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2018187172A</a>                                                                                                                                                               | 公开(公告)日 | 2018-11-29 |

| 申请号            | JP2017093368                                                                                                                                                                                | 申请日     | 2017-05-09 |

| [标]申请(专利权)人(译) | 奥林巴斯株式会社                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 奥林巴斯公司                                                                                                                                                                                      |         |            |

| [标]发明人         | 斎藤匡史                                                                                                                                                                                        |         |            |

| 发明人            | 斎藤 匡史                                                                                                                                                                                       |         |            |

| IPC分类号         | A61B1/04 A61B1/05 A61B1/00 G02B23/24                                                                                                                                                        |         |            |

| FI分类号          | A61B1/04.530 A61B1/05 A61B1/00.680 G02B23/24.B                                                                                                                                              |         |            |

| F-TERM分类号      | 2H040/CA04 2H040/CA11 2H040/CA22 2H040/DA02 2H040/DA11 2H040/DA12 2H040/DA14 2H040 /DA15 2H040/DA21 2H040/GA02 2H040/GA11 4C161/CC06 4C161/DD03 4C161/FF45 4C161/JJ11 4C161/LL02 4C161/SS03 |         |            |

| 代理人(译)         | 伊藤 进<br>长谷川 靖<br>ShinoUra修                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                   |         |            |

## 摘要(译)

要解决的问题：在图像拾取元件启动时校正电流消耗的意外减小状态，并且在激活时和正常操作时稳定电流消耗。根据预定控制信号流过VDD线的电流；以及设置在图像拾取元件中并从电源向图像拾取元件提供预定电源电压的控制电路，在图像拾取元件激活时流过VDD线的电流被设置为图像拾取元件的正常值电源电流控制单元160产生预定的控制信号，用于在操作期间相对增加在VDD线中流动的电流，并在预定的定时将控制信号输出到电源电流校正单元150；，包括：a。